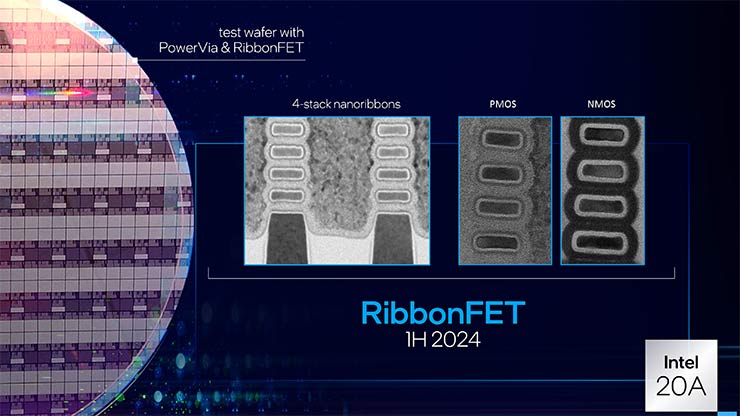

Intel promuove e accelera le innovazioni dei processi produttivi e del packaging per i prossimi prodotti e presenta RibbonFET e PowerVia. RibbonFET, è la prima nuova architettura di transistor in oltre 10 anni. Invece PowerVia è la prima soluzione di alimentazione attraverso il backside nel settore. L’azienda ha evidenziato la rapida adozione della litografia extreme ultraviolet (EUV) di nuova generazione, chiamata High Numerical Aperture (High NA) EUV. Intel sta per ricevere il primo strumento di produzione High NA EUV del settore.

Innovazione tecnologie di packaging

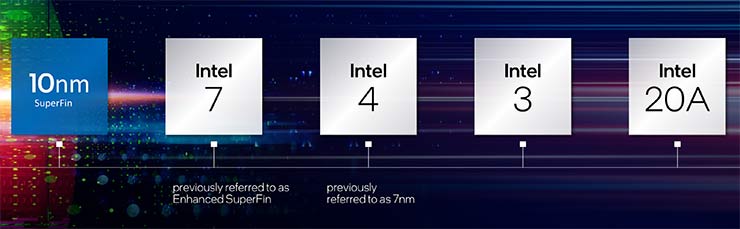

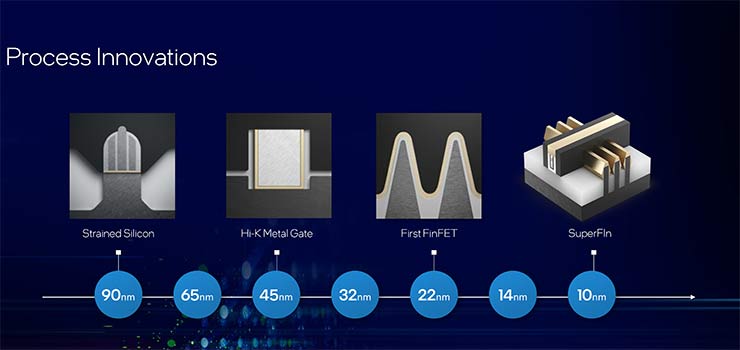

Il settore tecnologico ha da tempo riconosciuto che la tradizionale nomenclatura dei nodi di processo basata sui nanometri ha smesso di corrispondere alle effettive misure di lunghezza dei gate nel 1997. Oggi Intel presenta una nuova nomenclatura per i nodi di processo creando un quadro chiaro e omogeneo che offra ai clienti una visione più precisa dei nodi di processo esistenti nel settore. Questa chiarezza è più importante che mai con il lancio di Intel Foundry Services.

I tecnici di Intel hanno descritto la seguente roadmap con la nuova nomenclatura dei nodi e le innovazioni alla base di ciascuno di essi:

- Intel 7 offre un aumento di prestazioni per watt compreso tra il 10% e il 15% circa rispetto a Intel SuperFin a 10 nm, in base alle ottimizzazioni dei transistor FinFET.

- Intel 4 abbraccia appieno la litografia EUV per stampare elementi di dimensioni incredibilmente ridotte utilizzando luce a lunghezza d’onda ultracorta.

Innovazione tecnologie di packaging

- Intel 3 sfrutta ulteriori ottimizzazioni di FinFET e un aumento dell’EUV per fornire un aumento di circa il 18% nelle prestazioni per watt rispetto a Intel 4.

- Intel 20A inaugura l’era dell’angstrom con due tecnologie innovative, RibbonFET e PowerVia. RibbonFET sarà la prima nuova architettura di transistor dell’azienda da quando ha introdotto FinFET nel 2011.

Intel è inoltre entusiasta dell’opportunità di collaborare con Qualcomm con la propria tecnologia di processo Intel 20A.

2025 e oltre

Oltre a Intel 20A, Intel 18A è già in fase di sviluppo per l’inizio del 2025 con perfezionamenti a RibbonFET. Esse offriranno un ulteriore importante salto nelle prestazioni dei transistor. Intel sta inoltre lavorando per definire, costruire e distribuire High NA EUV di nuova generazione. L’azienda sta collaborando strettamente con ASML per assicurare il successo di questa svolta per il settore che supera l’attuale generazione di EUV.

Con la nuova strategia IDM 2.0 di Intel, il packaging sta diventando sempre più importate per realizzare i vantaggi della Legge di Moore. Intel ha annunciato che AWS sarà il primo cliente a utilizzare le soluzioni di packaging IFS, e ha fornito i seguenti dettagli sulla propria roadmap di packaging avanzato:

EMIB continua a guidare il settore come la prima soluzione di bridge embedded 2.5D, con prodotti in produzione dal 2017. Sapphire Rapids sarà il primo prodotto per datacenter Xeon a essere commercializzato in massa con EMIB (embedded multi-die interconnect bridge).

Innovazione tecnologie di packaging

- Foveros sfrutta le capacità di packaging a livello di wafer per fornire una soluzione di 3D stacking unica nel suo genere.

- Foveros Omni inaugura la nuova generazione della tecnologia Foveros fornendo flessibilità illimitata con la tecnologia di 3D stacking ad alte prestazioni per interconnessione die-to-die e prodotti modulari.

- Innovazione Foveros Direct passa all’unione diretta rame-rame per interconnessioni a bassa resistenza e rende più labile il confine tra dove finisce il wafer e dove inizia il package.