Sangfor Technologies rende disponibile una funzionalità avanzata per ottimizzare costi e prestazioni di Sangfor Virtualization Stack (HCI): il Memory Tiering su NVMe.

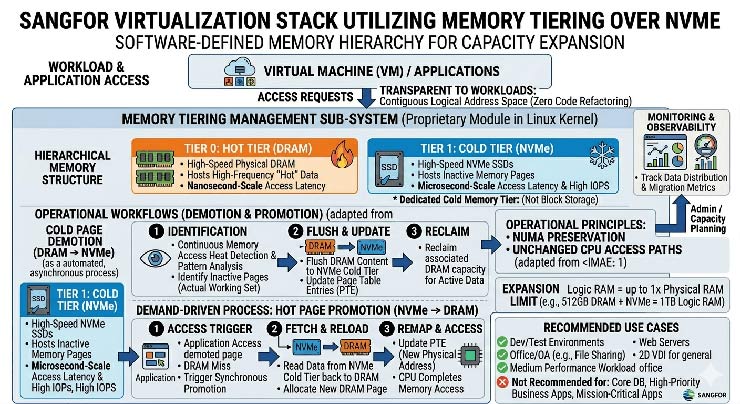

L’architettura è strutturata in due livelli distinti, gestiti da un modulo proprietario integrato nel kernel Linux. Il Tier 0, o “Hot Tier”, corrisponde alla DRAM fisica ad alta velocità, che ospita i dati “caldi” ad alta frequenza di accesso. Il Tier 1, o “Cold Tier”, è costituito da SSD NVMe ad alte prestazioni utilizzati come livello di archiviazione per le pagine di memoria inattive. In questa gerarchia, il dispositivo NVMe non è trattato come storage tradizionale, ma funziona come un livello di memoria “fredda” dedicato, con latenza di accesso nell’ordine dei microsecondi e valori di IOPS elevati per garantire reattività durante lo scambio frequente di pagine da 4KB.

Gestione e funzionamento

Il modulo di gestione del memory tiering integra tre capacità tecniche principali. Prima, l’identificazione dei dati caldi e freddi, grazie a un monitoraggio continuo degli accessi e all’analisi dei pattern, per distinguere accuratamente l’insieme di lavoro attuale (Actual Working Set). Secondo, la migrazione della memoria: le pagine inattive vengono declassate dalla DRAM al livello NVMe, liberando capacità per i dati più attivi, mentre le pagine calde vengono promosse nuovamente in DRAM al momento dell’accesso, aggiornando la mappatura della memoria. Terzo, il monitoraggio e l’osservabilità, che permettono di tracciare la distribuzione dei dati e le metriche di migrazione, aiutando gli amministratori a individuare eventuali colli di bottiglia e a pianificare efficacemente la capacità.

I principi operativi e la trasparenza

Il sistema è completamente trasparente per applicazioni e macchine virtuali, che continuano a vedere la memoria come uno spazio contiguo senza necessità di modifiche al codice. In caso di accesso a una pagina presente in DRAM, la latenza rimane nell’ordine dei nanosecondi; in caso di “DRAM Miss”, viene attivata una promozione sincrona prima di restituire i dati alla CPU. Il meccanismo rispetta l’architettura NUMA, privilegiando la DRAM locale e posizionando correttamente le pagine promosse. Lo stack supporta l’espansione della RAM logica fino a un massimo pari a una volta la RAM fisica: ad esempio, 512GB di DRAM combinati con un disco NVMe possono fornire fino a 1TB di RAM logica.