Le innovazioni tecnologiche rafforzano la capacità di Intel Foundry di contribuire a ripristinare la leadership nella produzione di chip negli Stati Uniti.

In occasione dell’IEEE International Electron Devices Meeting (IEDM) 2024, Intel Foundry ha presentato nuove scoperte per aiutare a far avanzare l’industria dei semiconduttori nel prossimo decennio e oltre. Intel Foundry ha presentato nuovi materiali che aiutano a migliorare le interconnessioni all’interno di un chip, ottenendo una capacità fino al 25% utilizzando il rutenio sottrattivo. Intel Foundry è stata anche la prima a segnalare un miglioramento del throughput utilizzando una soluzione di integrazione eterogenea per il packaging avanzato, per consentire l’assemblaggio chip-to-chip ultraveloce.

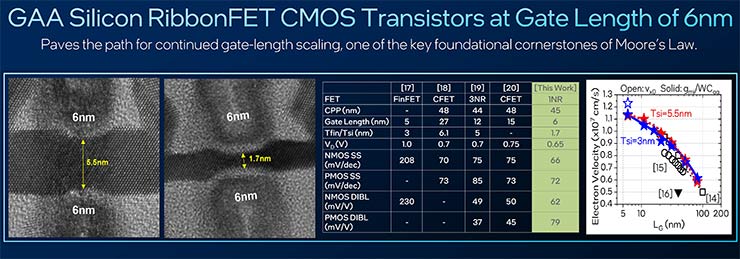

Per promuovere ulteriormente la scalabilità GAA (gate-all-around) e migliorare le prestazioni dei dispositivi, Intel Foundry ha dimostrato lavorazioni con il CMOS RibbonFET al silicio e con il modulo di ossido di gate per FET 2D scalati.

Mentre l’industria si dirige verso l’installazione di 1 trilione di transistor su un chip entro il 2030, le scoperte nella scalabilità dei transistor e delle interconnessioni sono fondamentali per soddisfare l’infinito desiderio di applicazioni informatiche più efficienti dal punto di vista energetico, ad alte prestazioni e convenienti.

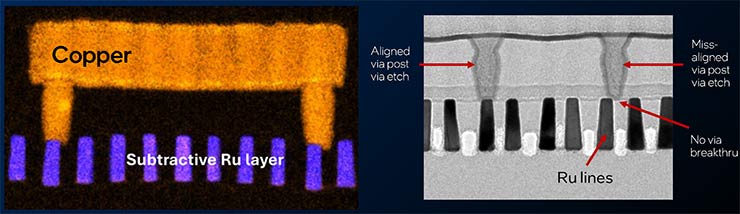

Intel Foundry ha identificato diversi percorsi che risolvono le limitazioni previste dei transistor in rame per la scalabilità dell’interconnessione per i nodi futuri:

- Rutenio sottrattivo (Ru): per migliorare le prestazioni e le interconnessioni all’interno dei chip, Intel Foundry ha presentato il rutenio sottrattivo, un nuovo materiale di metallizzazione alternativo che utilizza la resistività del film sottile insieme ai traferri per offrire un progresso significativo nella scalabilità delle interconnessioni. Il team ha sviluppato un processo integrato Ru sottrattivo pratico, economico e compatibile con la produzione di grandi volumi.

L’implementazione di traferri con Ru sottrattivo ha fornito fino al 25% di riduzione della capacità da linea a linea a passi inferiori o uguali a 25 nanometri (nm).

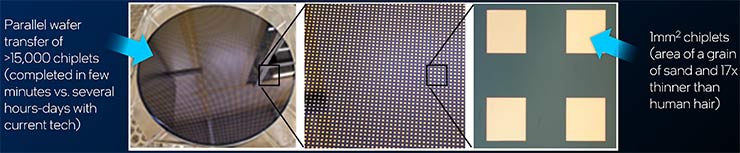

- Trasferimento selettivo degli strati (SLT): per consentire una produttività fino a 100 volte superiore per l’assemblaggio chip-to-chip ultraveloce in package avanzati, Intel Foundry è la prima a presentare il trasferimento selettivo degli strati (SLT), una soluzione di integrazione eterogenea che consente di realizzare chiplet ultrasottili con una flessibilità molto migliore, per consentire die di dimensioni inferiori e rapporti di aspetto più elevati rispetto al tradizionale legame chip-wafer.

- Silicon RibbonFET CMOS: Intel Foundry ha presentato i transistor CMOS al silicio RibbonFET con una lunghezza del gate di 6 nm.

- Gate Oxide per FET GAA 2D scalati: l’azienda ha presentato il suo lavoro sulla fabbricazione di transistor GAA 2D NMOS e PMOS con lunghezza del gate scalata fino a 30 nm con un focus specifico sullo sviluppo del modulo di ossido di gate (GOx). La ricerca riporta i risultati del settore studio di semiconduttori bidimensionali (2D) di dicalcogenuri di metalli di transizione (TMD), che potrebbero essere un futuro sostituto del silicio nei processi avanzati dei transistor.

Inoltre, Intel Foundry ha continuato a far progredire la ricerca con la prima tecnologia del settore al nitruro di gallio (GaN) da 300 millimetri, una tecnologia emergente per l’elettronica di potenza e a radiofrequenza in grado di offrire prestazioni più elevate e sostenere tensioni e temperature più elevate rispetto al silicio.

Si tratta dei primi MOSHEMT GaN (transistor ad alta mobilità elettronica a semiconduttore a base di metallo-ossido) in scala ad alte prestazioni del settore, fabbricati su un substrato GaN-on-TRSOI (“trap-rich” silicon-on-insulator) da 300 mm. Substrati avanzati come GaN-on-TRSOI possono ottenere prestazioni migliori in applicazioni come RF ed elettronica di potenza, riducendo la perdita di segnale e ottenendo una migliore linearità del segnale e consentendo schemi di integrazione avanzati che possono essere realizzati attraverso l’elaborazione del substrato posteriore.